## Agilent E2960 PCI Express

User Guide

Agilent Technologies

### Important Notice

© Agilent Technologies, Inc. 2004

### Manual Part Number E2960-91020

### Revision

November 2004

Printed in Germany

Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany Authors: t3 medien GmbH Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### Technology Licenses

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

### Safety Notices CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

### WARNING/DANGER

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Trademarks

Windows NT <sup>®</sup> and MS Windows <sup>®</sup> are U.S. registered trademarks of Microsoft Corporation.

## Content

| About this Guide   |                                                                          | 5  |

|--------------------|--------------------------------------------------------------------------|----|

| System Overview    |                                                                          | 7  |

|                    | Intended Use                                                             | 8  |

|                    | The Protocol Exerciser for PCI Express                                   | 10 |

|                    | The Protocol Analyzer for PCI Express                                    | 11 |

|                    | Software Components                                                      | 12 |

|                    | Session Concept                                                          | 14 |

|                    | Starting and Configuring a Session                                       | 15 |

|                    | Using a Session at Several Computers                                     | 15 |

| Running Your First | Tests                                                                    | 17 |

|                    | Testing the Communication to an Add-In Card                              | 18 |

|                    | Establishing an Exerciser Session                                        | 19 |

|                    | Establishing a PCI Express Link                                          | 23 |

|                    | Sending a Single Data Packet                                             | 25 |

|                    | What Happens at the Exerciser when sending a Single<br>Packet?           | 28 |

|                    | Analyzing the Communication to an Add-In Card                            | 30 |

|                    | Establishing an Analyzer Session                                         | 31 |

|                    | Setting Up a Trigger                                                     | 33 |

|                    | Starting the Analyzer                                                    | 36 |

|                    | Validating the System                                                    | 38 |

|                    | Setting Up the Trigger for the System Validation Test                    | 40 |

|                    | Writing Data to the Protocol Exerciser's Data Memory                     | 43 |

|                    | Setting Up and Running Block Transfers                                   | 44 |

|                    | Viewing the Results Using the User Interface                             | 49 |

|                    | What Happens at the Exerciser when transferring a Block?                 | 52 |

|                    | Bringing Up and Debugging a PCI Express Add-In Card                      | 53 |

|                    | Setting Up the Trigger for the Bring Up and Debug Test                   | 55 |

|                    | Modifying Specific Link Settings                                         | 59 |

|                    | Running the Test and Viewing the Results for the Bring Up and Debug Test | 60 |

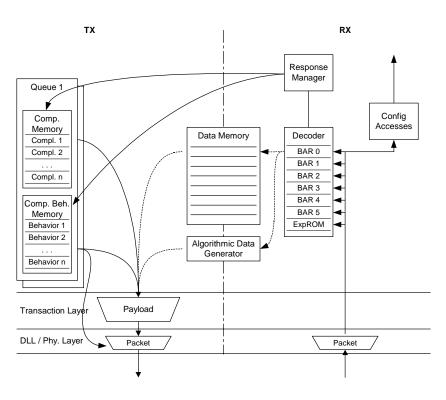

| Exerciser Architecture Overview                      | 61 |

|------------------------------------------------------|----|

| Exerciser as Requester                               | 62 |

| Exerciser as Completer                               | 65 |

| Exerciser Components                                 | 67 |

| How to Program the Exerciser and Analyzer            | 69 |

| Using the DCOM API                                   | 70 |

| Opening a New Session                                | 71 |

| Accessing a Running Session                          | 72 |

| Controlling the Exerciser from a SUT                 | 73 |

| Differences between the PCIe Port API and DCOM API   | 73 |

| Working with the PCIe Port API                       | 74 |

| Example of Using the In-System Port                  | 75 |

| Appendix                                             | 77 |

| Starting an Exerciser Session                        | 77 |

| Establishing a Link                                  | 79 |

| Sending a Single Packet                              | 80 |

| Starting an Analyzer Session                         | 82 |

| Downloading a Trigger Setup File to the Analyzer     | 83 |

| Writing Data to the Protocol Exerciser's Data Memory | 84 |

| Setting Up and Running Block Transfers               | 85 |

| Modifying Link Settings on the Exerciser             | 89 |

|                                                      | 07 |

# About this Guide

This Guide provides you with the information you need to get started working with the Agilent test solution for PCI Express. It contains the following chapters:

• "System Overview" on page 7

Briefly explains the main concepts behind the Agilent test solution for PCI Express.

- *"Running Your First Tests" on page 17* Provides some examples for using the Agilent test solution for PCI Express.

- "Exerciser Architecture Overview" on page 61

Explains how the Exerciser is structured and gives an overview as to how it works as a requester and completer.

• *"How to Program the Exerciser and Analyzer" on page 69* Explains how the Agilent test solution for PCI Express can be used programmatically.

The instructions in this Guide assume a correctly running system (controller PC up and running, software correctly installed on the clients). See the *Getting Started and Installation Guide* for details.

Literature General and detailed information on PCI Express can be obtained from Intel (*http://www.intel.com/technology*) and the PCI-SIG web site (*http://www.pcisig.com*).

> Features and technical data of the Agilent PCI Express hardware and software are published in the data sheet "Agilent Technologies E2960 Series Exerciser and Protocol Analyzer for PCI Express", publication number 5988-8679EN.

Updated product information For updated product information, please visit also http://www.agilent.com/find/E2960\_series.

# System Overview

PCI Express is designed to replace the PCI bus as the main I/O expansion bus in a wide range of systems. The multi-drop parallel bus approach of PCI is being replaced with a high-speed serial I/O bus that uses point-to-point signaling and a packetized protocol. The PCI Express architecture is scalable and extensible, and includes a rich set of features.

With the E2960 series, Agilent Technologies provides a family of Protocol Analyzers and Exercisers for PCI Express designed to support the increased need for analysis and validation of PCI Express chipsets and systems.

The Agilent test solution for PCI Express is a combined software/hardware solution.

The following sections provide you with an overview of the Agilent solution, its software components, and how they work together:

- "Intended Use" on page 8

- "Software Components" on page 12

- "Session Concept" on page 14

## **Intended Use**

Background Today's key trends in the electronics industry aim for smaller and smaller chip geometries and CMOS technology being able to run at higher and higher frequencies. The pin count needed for parallel busses prevents the industry to take full advantage of these technology developments (pad versus gate limitations). Moving from parallel to serial busses will help the industry to focus on further integration in functionality and resulting cost reductions.

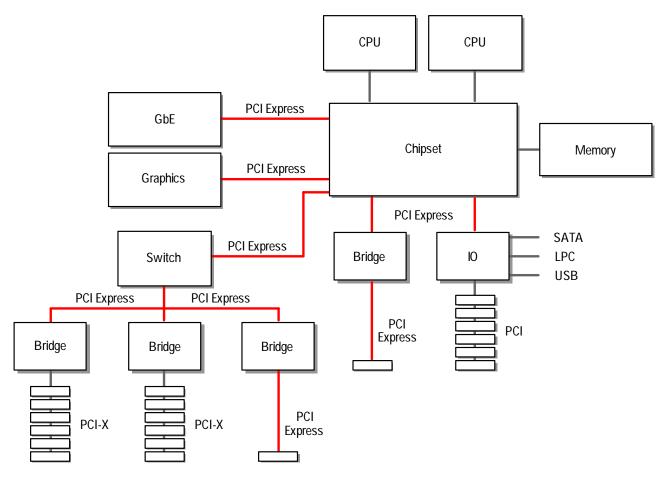

|                      | PCI Express, a protocol introduced to the public in 2002, will change<br>the way computer systems will be built in the near future. PCI Express<br>operates at 2.5 GBit/s and uses two low voltage differential signals<br>(LVDS) lines for transmitting and receiving data. Such a four-wire<br>connection, called a PCI Express link x1 (pronounced: by one), is the<br>foundation of PCI Express. Several of these links can be combined to<br>provide higher bandwidth. The specification calls out for PCI Express<br>x1, x2, x4, x8, x16 and x32. A by eight PCI Express link (x8) features a<br>bandwidth of 40 Gbit/s. |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | The previous figure illustrates a two-way server architecture based on<br>PCI Express. All key elements of the server (Chipset, Ethernet,<br>Graphics core) are connected via PCI Express. Different link widths<br>(x1, x4, x8, x16) are used to accompany the necessary bandwidth<br>needs. Traditional IO standards like PCI or PCI-X are connected with<br>bridges to PCI Express. Switches will be used to route PCI Express<br>traffic in such an architecture.                                                                                                                                                          |

| Test requirements    | The move from parallel busses to serial busses will result in different analysis and validation needs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | • Higher frequencies require enhanced test considerations on the physical layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | • Point-to-point connections require enhanced probing solutions as well as different analyzer and stimulus (exerciser) tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      | • Complexer system components require different test methodology with increased focus on protocol testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| The Agilent solution | With the E2960 series, Agilent Technologies provides a family of<br>Protocol Analyzers and Exercisers for PCI Express designed to<br>support this increased need for analysis and validation.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      | The E2960 series provides two types of testers:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | • Protocol Exerciser for PCI Express (x1 to x8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | • Protocol Analyzer for PCI Express (x1 to x8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      | Both tools are based on the same Serial I/O Module and probes,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Both tools are based on the same Serial I/O Module and probes, combined with unique software packages.

## The Protocol Exerciser for PCI Express

The Protocol Exerciser for PCI Express is able to generate and respond to all types of PCI Express transactions. In addition, it allows you to create various PCI Express protocol variations and violations.

Another key feature is the ability to insert errors and test the behavior of designs in response to these errors. Errors can be generated and inserted on the physical, data link, and transaction layers.

The Protocol Exerciser for PCI Express is controlled by a graphical user interface, a C/C++ program or a Tcl script.

With these features and more, the Protocol Exerciser for PCI Express is perfectly suited for:

Validating PCI Express systems

You can use the Protocol Exerciser to validate a PCI Express system (*Upstream* testing).

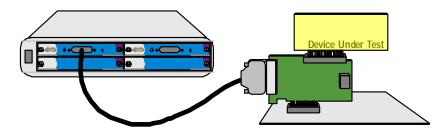

Figure 2 Protocol Exerciser Setup for Testing a System (To Upstream)

Bringing up and debugging PCI Express devices

You can use the Protocol Exerciser to bring up and debug a device (*Downstream* testing).

Figure 3 Protocol Exerciser Setup for Testing a Device (To Downstream)

The Protocol Exerciser functionality includes testing the physical and data link layer capabilities of a PCI Express device as well as simulating such devices on the transaction layer.

The Protocol Exerciser for PCI Express is also well suited for validating the inter-operability and stability of chipsets and systems.

## **The Protocol Analyzer for PCI Express**

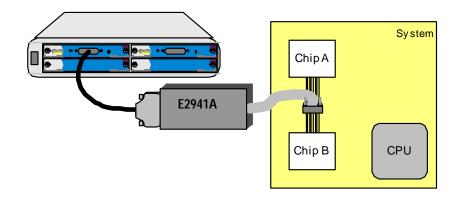

The Protocol Analyzer for PCI Express is used for capturing and analyzing the traffic between two PCI Express endpoints:

Listening to a system and add-in card

You can insert the Protocol Analyzer between a device and a system to capture the traffic.

Listening to two chips on a motherboard

You can connect the Protocol Analyzer to a midbus footprint on the motherboard to listen to the traffic between two chips. See the data sheet for the E2941A Midbus Probe for details.

## Figure 5 Protocol Analyzer Setup for Testing Communication between two Chips

The Protocol Analyzer captures traffic simultaneously from both directions, including training sequences, packets on the data link layer (DLLPs), and packets on the transaction layer (TLPs). It has 1 GB of trace memory.

The Protocol Analyzer for PCI Express includes a sophisticated trigger sequencer. Its graphical user interface allows you to filter the captured data and to view and investigate the packets in a variety of formats. It can also be controlled by a C/C++ program or a Tcl script.

With these features, the Protocol Analyzer for PCI Express is perfectly suited for testing and troubleshooting PCI Express links.

## **Software Components**

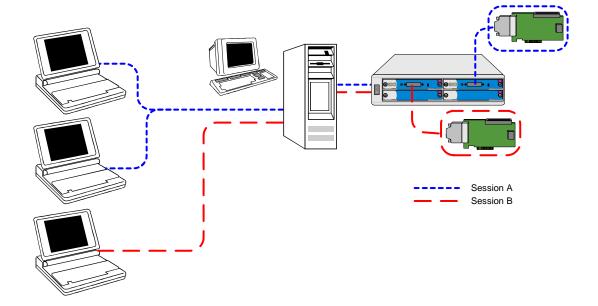

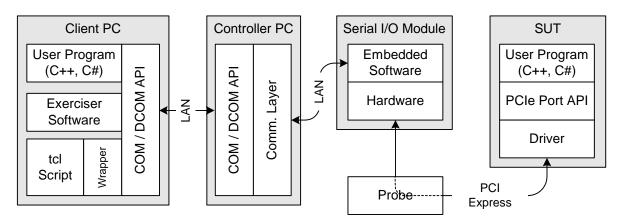

The Agilent test solution for PCI Express contains several advanced software components that work together:

• Firmware

Runs on the Serial I/O module Responsible for carrying out the actual tests

Controlled by the control software running on the controller PC

• Control software

Runs on the controller PC

Responsible for setting up and maintaining communication with the  $\rm I/O$  module, loading tests to the  $\rm I/O$  module

Controlled by the user software

$\bullet \ User \ software$

Runs on the client (local PC)

Responsible for setting up tests

Controlled by the user or programmer

The user software can be either the Agilent Protocol Exerciser and Protocol Analyzer software, or a tcl script or DCOM-based test program. Clients with User Software Exerciser / Analyzer SW tol Scripts DCOM-based Programs

The following figure illustrates the relationships between these software components:

Figure 6 PCI Express Software Components

**NOTE** Note that the user software can also run on the controller PC. In this case, the controller PC can be seen as its own client.

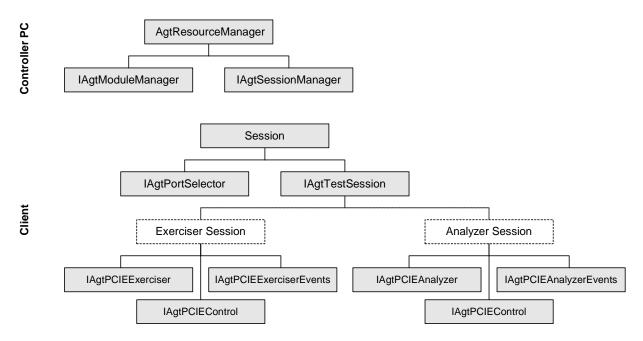

## **Session Concept**

The communication between the controller PC and the Serial I/O Modules is based on the concepts of *sessions*. A session is a representation of the instrument components involved in a test:

- The control software running on the controller PC

- The Serial I/O Module and the probe involved in the test

The following figure indicates the components involved in a session. It also indicates how more than one client can log onto one session.

To use a session, it is necessary to:

• Start and configure the session

This establishes communication between the client and the control PC and loads the necessary firmware onto the desired Serial I/O Module, which then assumes the personality required for the session (for example, Exerciser in upstream mode).

• End the session

In the Exerciser and Analyzer software, when you quit using a session and you are the last one using the session, you are prompted as to whether the session should be ended. Ending a session clears the Serial I/O Module, allowing it to be used for a new session.

All accesses to the test system must go over the session. The session is not locked: concurrent access to one session is possible. This is described under *"Using a Session at Several Computers" on page 15.*

## Starting and Configuring a Session

When the user software is started, it queries the control software running on the controller PC for a list of currently running sessions of the corresponding type (for example, a query by the Protocol Exerciser software returns a list of Exerciser-based sessions). The user software can either connect to one of these existing sessions, or request a new session.

If a new session is requested, the following occurs:

- 1. The user requests a session of a particular type (Exerciser or Analyzer).

- 2. The user adds a Serial I/O Module and its port (to the probe) to the session.

- 3. The Serial I/O Module downloads the necessary FPGAs and embedded software from the control PC.

- 4. The embedded software running on the Serial I/O Module configures the probe as necessary.

See "Opening a New Session" on page 71 to learn how to start and configure a session in your own program.

## Using a Session at Several Computers

If a session is up and running, you can use it from multiple instances of the user interface (for example, from different clients) or from tcl scripts or DCOM-based programs simultaneously. This could be necessary if you, for example, want to set up a test system directly at the controller PC and then run a series of tests from your PC.

The controller PC does not protect against meaningless or even conflicting requests. It is therefore recommended that only one user should "own" a particular session at a time.

To connect to a current session in the user interface, you only need to note the session number and then select this session when the software starts.

See *"Accessing a Running Session" on page 72* to learn how to connect to a running session in your own program.

# **Running Your First Tests**

The following sections guide you step-by-step through your first tests with Agilent test solution for PCI Express:

- *"Testing the Communication to an Add-In Card" on page 18* This test demonstrates how you set up communication between a probe board to be used as an Exerciser and a PCI Express add-in card that you would like to test. With the information here, you should also be able to set up tests between a probe board and a PCI Express system.

- *"Analyzing the Communication to an Add-In Card" on page 30* This test shows you how you capture PCI Express communication between an add-in card and another probe board as Exerciser by using a probe board as Analyzer.

- "Validating the System" on page 38

With this test, you see how you can analyze how a PCI Express system responds to requests with different behaviors and errors.

• "Bringing Up and Debugging a PCI Express Add-In Card" on page 53

With this test, you see how you can verify the correct behavior of an add-in card during link training when the requester changes link settings.

# Testing the Communication to an Add-In Card

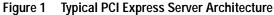

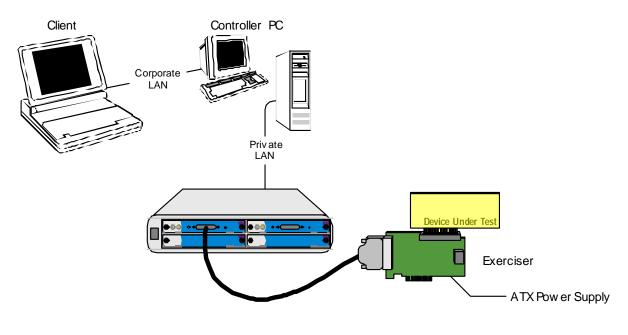

For this test, we want to set up a PCI Express link between a probe board and an add-in card (for example, graphic card) and then test how the add-in card reacts to an errored packet.

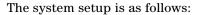

System Setup The following system setup is required for this test:

- The add-in card to be tested is plugged into the PCI Express slot at the top of the probe board.

- The Serial I/O Module to which the probe board is connected is set up as a Protocol Exerciser.

- An external ATX power supply is connected to the probe board. The power jumper on the probe board should be set to **Ext** (instead **sys**).

The external power supply is required to power the add-in card. Alternatively, you could plug the probe board into a powered PCI Express slot and set the jumper to **sys**.

The system setup is as follows:

Figure 8 Protocol Exerciser Setup for Testing a PCI Express Add-In Card (To Downstream)

| How to Proceed | This test is carried out as follows:                                                                                                                                                        |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                | 1. We establish an Exerciser session at the client. This establishes the necessary communication and sets up the Serial I/O Module (with probe) to be used as an Exerciser.                 |  |  |  |

|                | See "Establishing an Exerciser Session" on page 19.                                                                                                                                         |  |  |  |

|                | 2. We set up and establish a PCI Express link between the Exerciser and the add-in card.                                                                                                    |  |  |  |

|                | See "Establishing a PCI Express Link" on page 23.                                                                                                                                           |  |  |  |

|                | 3. We set up the Exerciser to perform a data read on the add-in card.<br>This is done by sending a data read request as a single packet to the add-in card.                                 |  |  |  |

|                | See "Sending a Single Data Packet" on page 25.                                                                                                                                              |  |  |  |

|                | Once you have carried out the test, see <i>"What Happens at the Exerciser when sending a Single Packet?" on page 28</i> to find out what happens internally in the Exerciser by such tests. |  |  |  |

| TCL Scripts    | The following TCL scripts correspond to the requirements of this example:                                                                                                                   |  |  |  |

|                | • "Starting an Exerciser Session" on page 77                                                                                                                                                |  |  |  |

|                | • "Establishing a Link" on page 79                                                                                                                                                          |  |  |  |

|                | • "Sending a Single Packet" on page 80                                                                                                                                                      |  |  |  |

## **Establishing an Exerciser Session**

Before you can run any tests with the Exerciser, you have to establish a session at the client. A session is responsible for the following:

- Communication between the client and controller PC

- Configuration of the Serial I/O Module and probe board

To start an Exerciser session from a client:

1 Start the PCI Express Protocol Exerciser software on your PC.

The software requires the network name or IP address of the controller PC so that it can communicate with the controller PC. The *Select type of connection* dialog box opens, which allows you to specify that you want to establish a new session and enter the network name (or IP address) of the controller PC.

| Select type of connection      | _ 🗆 🗡            |

|--------------------------------|------------------|

| Connection type                |                  |

| Connect to existing session    |                  |

| Connect to <u>n</u> ew session |                  |

| C Offline mode                 |                  |

| Session setting                |                  |

| Server localhost               | Get session list |

| Session list                   |                  |

|                                |                  |

|                                |                  |

|                                |                  |

|                                |                  |

| Start Exit                     | Help             |

### Figure 9 Select type of connection Dialog Box

2 Select *Connect to new session*, enter the network name of the controller PC under *Server* and then click *Start*.

The *Choose a Sessiontype* dialog box opens. This dialog box allows you to define the session type (upstream or downstream).

| 🚰 Choose a Sessiontype 🛛 🔀       |  |  |  |  |  |

|----------------------------------|--|--|--|--|--|

| What type of session to create ! |  |  |  |  |  |

| Perior Under<br>Test             |  |  |  |  |  |

| To Downstream                    |  |  |  |  |  |

| To Upstream                      |  |  |  |  |  |

| Cancel                           |  |  |  |  |  |

| L                                |  |  |  |  |  |

Figure 10 Choose a Sessiontype Dialog Box

**3** Because we are testing an add-in card, we need a downstream session. Click *To Downstream*.

The new session is started on the controller PC, the client connects to this session. When the connection has been established, the *Select port to open* dialog box opens. This dialog box indicates which Serial I/O Modules are ready to be used, and which are already in use. When starting a session, you can only select a module that is not in use.

| 🚰 Select port to use                                                          |                         |                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module/Port                                                                   | State                   | Type [                                                                                                                                                                                                                   |

| □     101       □     □       □     102/1       □     103/1       □     103/1 | in us<br>ready<br>ready | AGT_MODULE_ONEPORT_PCIEXPRES N<br>AGT_PORT_PCIEXPRESS_X8 N<br>AGT_MODULE_ONEPORT_PCIEXPRES N<br>AGT_PORT_PCIEXPRESS_X8 N<br>AGT_MODULE_ONEPORT_PCIEXPRES N<br>AGT_MODULE_ONEPORT_PCIEXPRES N<br>AGT_PORT_PCIEXPRESS_X8 N |

| OK Refresh                                                                    | list                    | <b>&gt;</b>                                                                                                                                                                                                              |

Figure 11 Select port to open Dialog Box

**4** Select the Serial I/O Module that is connected to the probe board and click *OK*. You can see the module number on the display on the front of the Serial I/O Module.

The embedded software and FPGA contents are now loaded onto the Serial I/O Module and the PCI Express Protocol Exerciser software starts.

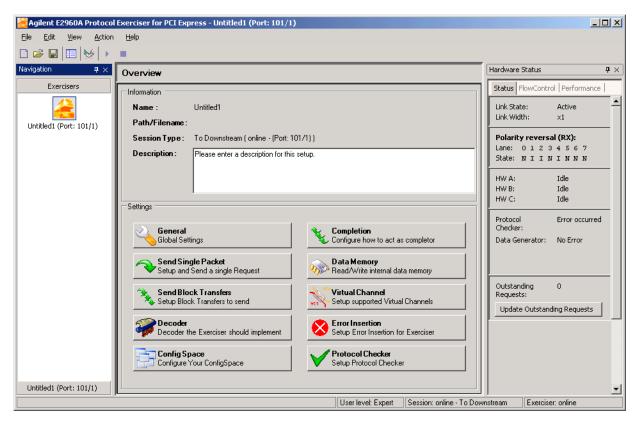

### Figure 12 PCI Express Protocol Exerciser Software

TIP Enter a description and save the setup by clicking the *Save* icon. You can then use this setup for later tests.

## **Establishing a PCI Express Link**

After you have established a session, you have to establish a PCI Express link to the add-in card. Depending on the add-in card, you may have to configure the link (for example, allowed link width).

To establish a PCI Express link:

1 Select the *General* icon on the Exerciser.

This opens the *General* card with the *Link Settings* tab on top, allowing you to configure the link. The *Hardware Status* informs you about the current link state. We can see here that the link is not up yet.

| General                                           |                                               |          |                                                     | Hardware Status               | <b>4</b> ×             |

|---------------------------------------------------|-----------------------------------------------|----------|-----------------------------------------------------|-------------------------------|------------------------|

| Link Settings Lane Settings                       | PatternMatcher   Trigger Out   Data Generator |          |                                                     | Status ElewContr              | ol Performance         |

|                                                   | ▼ x1 ▼ x2 ▼ x4 ▼ x8                           |          |                                                     | Link State:<br>Link Width:    | No Link<br>No Link     |

| Negotiated Link Width: No Link Scrambler: Enabled |                                               |          | Polarity reverse<br>Lane: 0 1 2 3<br>State: N N N 1 | 34567                         |                        |

| Clock source:                                     | internal                                      |          |                                                     | HW A:<br>HW B:                | Idle<br>Idle           |

| DUT Connectivity:<br>Session Type:                | Bench 💌<br>To Downstream                      |          |                                                     | HW C:<br>Protocol<br>Checker: | Idle<br>Error occurred |

|                                                   | Data Generator:                               | No Error |                                                     |                               |                        |

|                                                   |                                               |          |                                                     | Outstanding<br>Requests:      | 0                      |

|                                                   |                                               |          |                                                     | Update Outstan                | ding Requests          |

|                                                   |                                               |          |                                                     |                               |                        |

|                                                   |                                               |          |                                                     |                               |                        |

|                                                   | Apply                                         | Cancel   | Help                                                |                               | <b>-</b>               |

### Figure 13 Link Settings

2 Select the desired Supported Link Widths

This allows you to select which link widths the Exerciser will allow (x1, x2, x4, x8). The support of x1 is mandatory per PCI Express specification and is therefore always selected.

The *Negotiated Link Widths* indicates the link width the two partners have agreed upon after link up. The *Negotiated Link Widths* depend on the capabilities of the Exerciser and add-in card.

- 3 Select *Bench* for the *DUT Connectivity. To Downstream* should already be defined as the *Session Type*.

DUT Connectivity defines how the probe board is connected to the DUT (Bench or Platform).

- **NOTE** If you were testing a system, *To Upstream* should be selected for the *Session Type*.

- 4 If not already running, power up the add-in card.

- **5** Initiate link training by clicking *Link Up* in the *Action* menu.

The Exerciser now establishes communication with the add-in card. When the link state changes to *Active*, the link has been established.

The Exerciser is now ready for testing.

## Sending a Single Data Packet

Once we have established a link between the Exerciser and the add-in card, we can quickly perform a memory read on the add-in card by sending a read request as a *single packet*. The Exerciser software provides all standard PCI Express requests. The Exerciser software also allows you to define the request behavior so that specific errors are added to the packets to be transferred.

To send a single data packet:

1 Click the Send Single Packet icon.

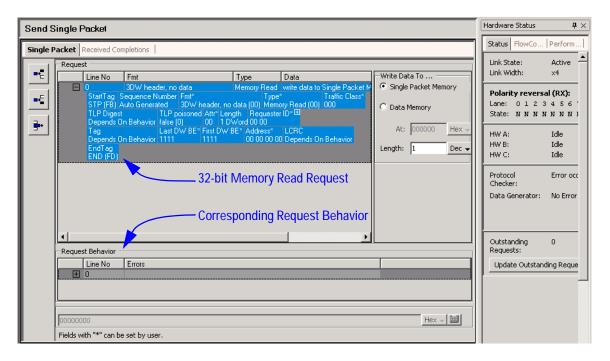

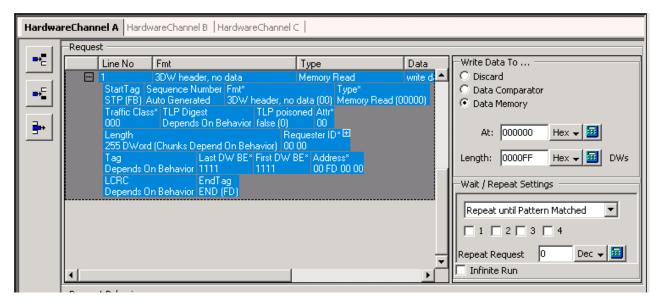

The *Send Single Packet* card opens with the *Single Packet* tab on top. A 32-bit *Memory Read* request with one corresponding request behavior is included.

### Figure 14 Send Single Packet Card

Note that you can add a request by clicking the Add Request icon.

•-⊑

2 If the PCI Express add-in card has special requirements (for example, the memory area available for access), change any of the request parameters marked with an asterisk (\*) as necessary.

In this example, we set the physical address to be read to 0x200000.

| Single P | acket  | Received Cor        | npletions                           |            |                                 |              |                 |

|----------|--------|---------------------|-------------------------------------|------------|---------------------------------|--------------|-----------------|

|          | Reques | st                  |                                     |            |                                 |              |                 |

|          |        | Line No             | Fmt                                 |            | Туре                            | Data         |                 |

|          |        |                     | 3DW header, no data                 |            |                                 |              | memory to addre |

| •-       |        |                     | equence Number Fmt*                 |            | Type*                           |              | Traffic Class*  |

|          |        | TLP Digest          | Auto Generated 3DW                  |            | data (UU) Memo<br>gth Requester |              | 000             |

|          |        | Depends 0           | n Behavior false (0)<br>Last DW BE* | 00 1 D     | Word 00 00                      |              |                 |

|          |        | Tag                 | Last DW BE*                         | First DW I | BE* Address*                    | LCRC         |                 |

|          |        | Depends D<br>EndTag | n Behavior 1111                     | 1111       | 00 20 00 00                     | ) Depends Or | n Behavior      |

|          |        | END (FD)            |                                     |            |                                 |              |                 |

|          |        |                     |                                     |            |                                 |              |                 |

|          |        |                     |                                     |            |                                 |              |                 |

|          |        |                     |                                     |            |                                 |              |                 |

|          |        |                     |                                     |            |                                 |              |                 |

|          |        |                     |                                     |            |                                 |              |                 |

|          |        |                     |                                     |            |                                 |              |                 |

|          | •      |                     |                                     |            | /                               |              | •               |

|          | Reques | st Behavior –       |                                     |            | /                               |              |                 |

|          |        | Line No             | Errors                              |            |                                 |              |                 |

|          | (H)    |                     | 2.1.0.0                             | /          |                                 |              |                 |

|          |        |                     | /                                   | /          |                                 |              |                 |

|          | Addres | ~                   |                                     |            |                                 |              |                 |

|          |        | -                   |                                     |            |                                 |              |                 |

|          | 002000 | 00                  |                                     |            |                                 |              |                 |

### Figure 15 Request Parameter Setting

**3** In *Request Behavior*, define the behavior so that the packet is sent with an incorrect LCRC by clicking *LCRC* in *Request Behavior* and then setting the *LCRC* to *Incorrect* in the field below.

Sending packets with errors allows you to check the packet verification of the add-in card. A packet with an incorrect LCRC must cause the add-in card to reply with a NAK. The Exerciser's replay algorithm then replays the packet with correct LCRC. This packet must then be acknowledged with an ACK by the add-in card.

| Request Behavior                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line No Errors                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                       |

| Automatic Tag TLP Dignet LCRC Disparity Payload Size TLP Poisoned TLP Nullified Replace STP<br>Automatic Tag (1) Marked Autent (0) Incorrect (1) Correct (0) Correct (0) Disabled (0) Disabled (0) Disabled (0)<br>Replace END Offset Sequence Number |

| Disabled (0) Disabled (0)                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

| LCRC                                                                                                                                                                                                                                                  |

| Incorrect Hex 🗸 🔛                                                                                                                                                                                                                                     |

| Correct                                                                                                                                                                                                                                               |

| Incorrect                                                                                                                                                                                                                                             |

| Enter value> Apply Cancel Help                                                                                                                                                                                                                        |

Figure 16 Single Packet with Incorrect LCRC

- 4 Click *Send Single Packet* in the *Action* menu to send the packet. The packet is first sent with the error. When the PCI Express system or the PCI Express add-in card returns a NAK (negativeacknowledge), the software sends the packet without the error.

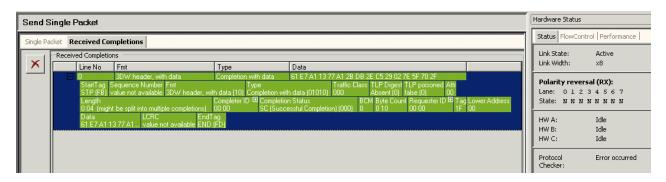

- 5 Click the *Received Completions* tab to view the completions.

The Exerciser stores completions to single packets and presents these in the *Received Completions* tab. This allows you to see how the add-in card responded to the read request.

### Figure 17 Received Completions

As you can see in this figure, the add-in card sent a completion with data. You do not see the NAK here, because a NAK is not a completion.

# What Happens at the Exerciser when sending a Single Packet?

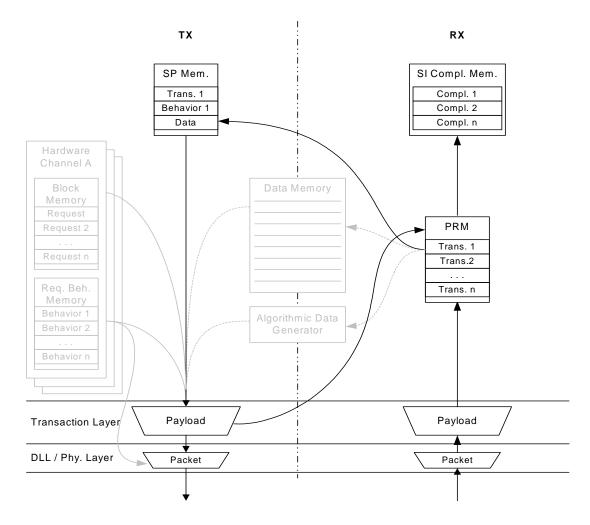

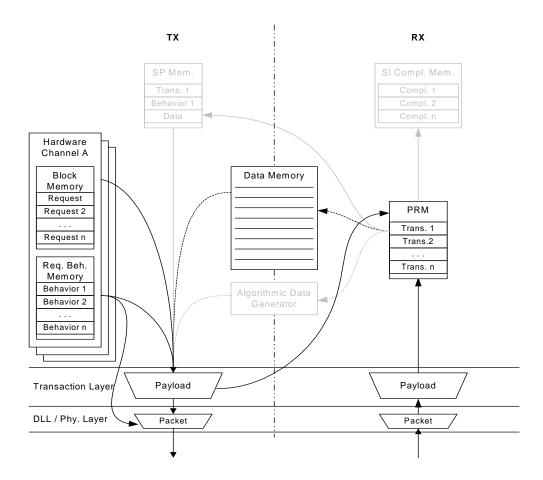

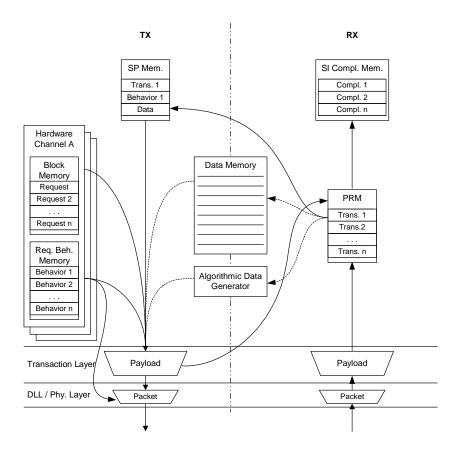

Familiarity with the internal structure of the Exerciser is helpful for understanding how the Exerciser works when sending a single packet. The following figure illustrates the Exerciser components involved in this task.

Figure 18 Exerciser as Requester (sending a single packet)

The Exerciser has a memory area for the *Send Single Packet* function (the *SP Mem.* in this figure). When you set up a single packet, the request, request behavior, and any data are written to this area. When you then send the single packet, the packet is assembled at the transaction layer according to the behavior and passed to the data link layer (DLL).

For any requests that expect a response (for example, a memory read), an entry is added in the Pending Request Map (PRM). The PRM keeps track of which responses are still open, which have been returned, and to which memory location returned data from responses should be written.

When a response is returned, the Exerciser looks up the request in the PRM and writes the transaction to the Send Immediate Completion Memory (SI Compl. Mem.). In the user software, this is shown in the *Returned Completions* window. It additionally writes any returned data to the memory location defined with the request (which is typically the Single Packet Memory).

If an error that forces a NAK has to be added to a packet (for example, wrong LCRC), the packet is sent once incorrectly. When the device or system under test returns a NAK, the packet is sent correctly.

See *"Exerciser as Requester" on page 62* for a detailed description of how the Exerciser acts as a requester.

## Analyzing the Communication to an Add-In Card

If you have a second Serial I/O Module with probe board and the PCI Express Protocol Analyzer software, you can additionally monitor the packets sent on the link. This allows you to analyze the contents of the individual packets, for example to see how the DUT responds to errored packets.

System Setup

- The following system setup is required for this test:

- The add-in card to be tested is plugged into the PCI Express slot at the top of the probe board set up as Analyzer.

- The Analyzer probe board is plugged into the PCI Express slot at the top of the probe board set up as Exerciser.

- An external ATX power supply is connected to the probe board. The power jumper on the probe board should be set to Ext (instead sys). The external power supply is required to power the add-in card. Alternatively, you could plug the probe board into a powered PCI Express slot and set the jumper to sys.

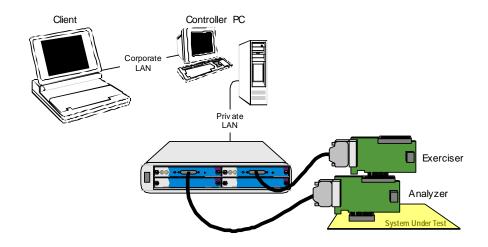

Figure 19 Protocol Analyzer Setup for Testing Communication with an Add-In Card

| How To Proceed | This test is carried out as follows:                                                                                                                                                                                                   |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                | <ol> <li>We have to establish an Exerciser session (described in<br/>"Establishing an Exerciser Session" on page 19) and an Analyzer<br/>session at the client.</li> <li>See "Establishing an Analyzer Session" on page 31.</li> </ol> |  |  |  |  |

|                | <ul><li>2. We set up a trigger on the Analyzer so that the Analyzer captures traffic around a specific packet.</li><li>See "Setting Up a Trigger" on page 33.</li></ul>                                                                |  |  |  |  |

|                | <ul><li>3. Once the trigger has been set up, we can start the Analyzer and view the captured traffic.</li><li>See "Starting the Analyzer" on page 36.</li></ul>                                                                        |  |  |  |  |

| TCL Scripts    | <ul><li>The following TCL scripts correspond to the requirements of this example:</li><li><i>"Starting an Analyzer Session" on page 82</i></li></ul>                                                                                   |  |  |  |  |

|                |                                                                                                                                                                                                                                        |  |  |  |  |

• "Downloading a Trigger Setup File to the Analyzer" on page 83

## **Establishing an Analyzer Session**

As with the Exerciser, you must first establish a session at the client.

To start an Anaylzer session:

Start the PCI Express Protocol Analyzer software on your PC. The software requires the network name or IP address of the controller PC so that it can communicate with the controller PC. The *Select type of connection* dialog box opens, which allows you to specify that you want to establish a new session and enter the network name (or IP address) of the controller PC.

| 🚝 Se | lect type of conne             | ection |          | _ 🗆 🗵    |

|------|--------------------------------|--------|----------|----------|

| Cor  | nnection type                  |        |          |          |

| 0.0  | Connect to <u>e</u> xisting se | ssion  |          |          |

| • 0  | Connect to <u>n</u> ew sessio  | n      |          |          |

| Οſ   | <u>)</u> ffline mode           |        |          |          |

| Ses  | sion setting                   |        |          |          |

| Ser  | ver localhost                  |        | Get sess | ion list |

| Sea  | ssion list                     |        |          |          |

|      |                                |        |          |          |

|      |                                |        |          |          |

|      |                                |        |          |          |

|      | Start                          | Exit   |          | Help     |

Figure 20 Select type of connection Dialog Box

**2** Select *Connect to new session*, enter the IP address or network name of the controller PC under *Server* and then click *Start*.

The client requests a new connection on the controller PC. When the connection has been established, the *Select port to open* dialog box opens with the module and port numbers of the Serial I/O Modules. Because we want to start a new session, we have to select one of the ports that is ready.

| <mark>e</mark> Select port t                     | o 💶 🗙                     |

|--------------------------------------------------|---------------------------|

| 101/1 (in use)<br>102/1 (ready)<br>103/1 (ready) |                           |

| Open port<br>Switch to Off                       | Refresh list<br>line-mode |

### Figure 21 Select port to open Dialog Box

**3** Select the port for the Serial I/O Module to be used as Analyzer and click *Open port*. The module numbers are on the display on the front of the module.

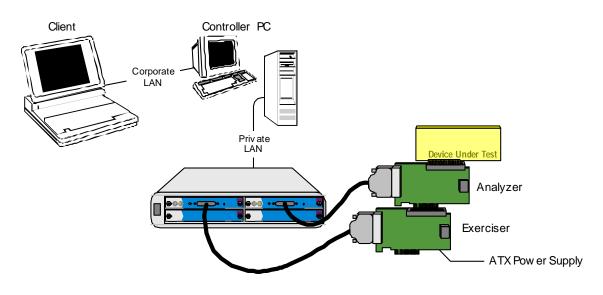

The embedded software and FPGA contents are loaded to the Serial I/O Module and the PCI Express Protocol Analyzer software starts.

### Figure 22 PCI Express Protocol Analyzer Software

The session has now been established. You can see this in the status bar at the bottom of the screen.

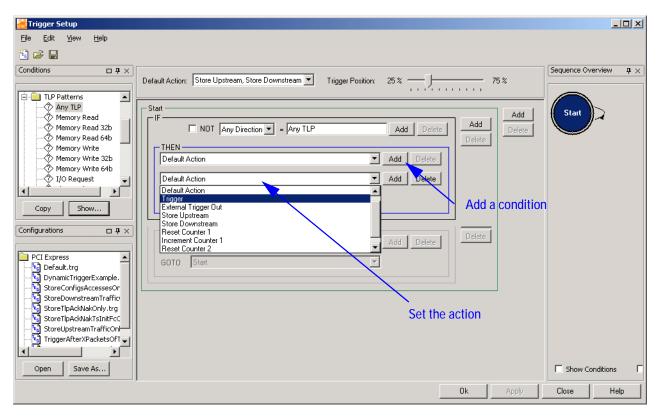

## Setting Up a Trigger

At this point, both the Exerciser and Analyzer software should be running on the client and sessions should be established to both Serial I/O Modules involved in the test.

It is now necessary to program the Analyzer so that it triggers (starts the capture of packets) upon the occurrence of a particular packet. To keep the test simple, we will set up the Analyzer so that it triggers upon the occurrence of a transaction layer packet (TLP). This us allows us to use the Exerciser as it was previously set up.

To set up the Analyzer to trigger upon occurrence of a TLP packet:

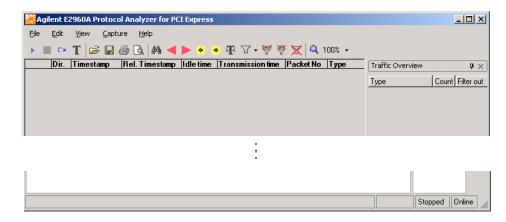

1 Click *Trigger Setup* in the *Capture* menu.

The *Trigger Setup* dialog box opens, which is used for setting up triggers.

2 On the left side in the *Trigger Setup* dialog box, you can see two columns with *Conditions* and *Configurations*. If these are not visible, check the corresponding items in the *View* menu.

| Default Action: Store Upstream, Store Downstream   PCI Express TRUE ExtTrigger In ProtocolError Counter1 Counter2 B Default Action IDE Patterns B Default Action Add Delete Edit Configurations PCI Express Start Default Action Add Delete Default Action Add Delete Default Action Add Delete Delete Edit Configurations <                                                                                    | 🚰 Trigger Setup                                                                                                                                |                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Conditions       9 ×         PCI Express       Trigger Position:       25 %         PCI Express       F       NOT TRUE         PCI Express       Add       Delete         Counter 1       Counter 2       Add         Configurations       Image: Configurations       Image: Configurations       Image: Configurations         PCI Express       Configurations       Image: Configurations       Image: Configurations       Image: Configurations         PCI Express       Configurations       Image: Configurations       Im | <u>File E</u> dit <u>V</u> iew <u>H</u> elp                                                                                                    |                                                                                                  |

| Default Action: Store Upstream, Store Downstream   PCI Express Counter1 ProtocolError Counter2 Int Patterns Default Action Add Default Action                                                                                                                                                                                                      | 19 😂 🖬                                                                                                                                         |                                                                                                  |

| PCI Express   TRUE   ProtocolError   Counter1   Counter2   B   Link Patterns   B   Link Patterns   B   Link Patterns   B   Default Action   Add   Default Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Conditions $\Box \mathbf{P} \times$                                                                                                            | Default Astien: Store Doumetream V Triang Reading: 25 % 75 %                                     |

| Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRUE     ExtTriggerIn     ProtocolError     Counter1     Counter2     TUP Patterns     DLIP Patterns     Link Patterns                         | Start<br>F<br>Start<br>F<br>NOT TRUE<br>Add Delete<br>Default Action<br>Add Delete<br>Add Delete |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Configurations Q X<br>PCI Express<br>PCI Express<br>PCI Express<br>PCI Express<br>PCI Express<br>PCI Express<br>Solution<br>StoreConfigeAcces: | THEN Add Delete                                                                                  |

| StoreTlpAckNakOnl     StoreTlpAckNakTsi       StoreUpstreamTraf     TriggerAfterXPacke       Open     Save As         Ok     Apply         Close     Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | StoreTlpAckNakOnl       StoreTlpAckNakTsIi       StoreUpstreamTraf       TriggerAfterXPacke                                                    |                                                                                                  |

The *Trigger Setup* dialog box should now appear as follows:

Figure 23 Trigger Setup Conditions

**3** The *Trigger Setup* dialog box is set up as a series of IF conditions that cause actions to be performed upon their occurrence.

To cause the Analyer to trigger upon occurrence of any TLP pattern, in the Conditions box, open the *TLP Patterns* folder and drag *Any TLP* into the condition field in the *Start* frame.

| 🚰 Trigger Setup                                                                                                                                                                                                                                                                                                                                        |                 |       |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|----------|

| <u>File E</u> dit <u>Vi</u> ew <u>H</u> elp                                                                                                                                                                                                                                                                                                            |                 |       |          |

|                                                                                                                                                                                                                                                                                                                                                        |                 |       |          |

| TLP Patterns       ▲         ▲ Any TLP         Memory Read         ●       Memory Read 64b         ●       Memory Write         ●       Memory Write 64b         ●       If         ■       If         ■       NOT Any Direction ■         ▲       Add Delete         ●       Memory Write 64b         ●       I/O Request         ■       I/O Request | e Add<br>Delete | 75 %  | Sequence |

| Copy Show                                                                                                                                                                                                                                                                                                                                              | Add             | 1     |          |

| Configurations                                                                                                                                                                                                                                                                                                                                         | 1 Delete        |       |          |

| Open Save As                                                                                                                                                                                                                                                                                                                                           |                 |       | Show     |

|                                                                                                                                                                                                                                                                                                                                                        | Ok              | Apply | Close    |

## Figure 24 Setting the Condition

4 The *Default Action* defines what to do if the set conditions are not met. Because we want to see all traffic that occurs, we set the *Default Action* to *Store Upstream, Store Downstream.*

| Default Action: Store Upstream, Store Downstream 💌 | Trigger Position: | 25% 75% |

|----------------------------------------------------|-------------------|---------|

Figure 25 Setting the Default Action

- **5** For our test, we want the Analyzer to trigger upon occurrence of a TLP. We also want the Analyzer to capture the TLP packet that triggers the capture as well. We must therefore:

- Add a condition to the THEN statement.

- Set the first action to *Default Action* (to capture the triggering packet).

- Set the second action to Trigger (to start the capture).

This is shown below:

Figure 26 Setting the Actions

**NOTE** Because we only have one IF condition, upon occurrence of the TLP, we go to Start (the only condition block).

| 🚰 Trigger Setup                                                                                                                            |                                                                                                                                                                                                                                                                                                                                              | _                 |            |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|

| <u>File E</u> dit <u>Vi</u> ew <u>H</u> elp                                                                                                |                                                                                                                                                                                                                                                                                                                                              |                   |            |

| 19 🚔 🔚                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                              |                   |            |

| Conditions                                                                                                                                 | Default Action:       Store Upstream, Store Downstream       Trigger Position:       25 %       75 %         Start       IF       NOT Any Direction       = Any TLP       Add       Delete         THEN       Default Action       Image: Add       Delete       Delete         Trigger       Add       Delete       Image: Add       Delete | Sequence Overview | <b>7</b> × |

| Copy Show<br>Configurations 4 ×<br>PCI Express<br>Default.trg<br>DynamicTriggerExample.<br>StoreConfigAccessesOr<br>StoreDownstreamTraffic | GOTO Stat                                                                                                                                                                                                                                                                                                                                    |                   |            |

| Store TipAckNakOnly.trg<br>Store TipAckNakTsInitFcC<br>StoreUpstreamTrafficOn<br>TriggerAfterXPacketsOfT                                   |                                                                                                                                                                                                                                                                                                                                              | Show Conditions   | <b>F</b>   |

|                                                                                                                                            | Ok Apply                                                                                                                                                                                                                                                                                                                                     | Close He          | IP I       |

The Analyzer appears as shown below:

Figure 27 Analyzer with Setup TLP Trigger

- **6** Click the *Save* icon, and give the trigger configuration file an appropriate name (for example, "test\_trigger\_on\_tlp.trg").

- 7 Click *OK* to apply the trigger and close the *Trigger Setup*.

## Starting the Analyzer

Once the trigger has been set up, we can start the Analyzer. When the Analyzer detects a TLP packet, it will trigger, allowing us to view any traffic that is captured.

To start the Analyzer:

- In the Protocol Analyzer software, click *Start* in the *Capture* menu. The Protocol Analyzer now tracks the packets sent through the bus.

- 2 In the Protocol Exerciser user interface, send a single data packet as described in *"Sending a Single Data Packet" on page 25.*

If any TLPs are sent, the Protocol Analyzer will trigger and fill the memory with traffic 25% before the trigger and 75% after the trigger.

You can now view the captured traffic in the Protocol Analyzer and verify if the behavior of the PCI Express system or add-in card in response to an incorrect LCRC is correct.

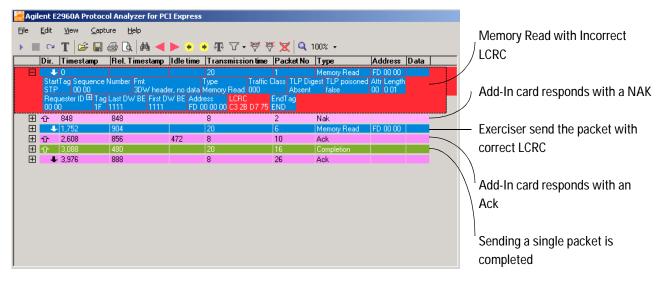

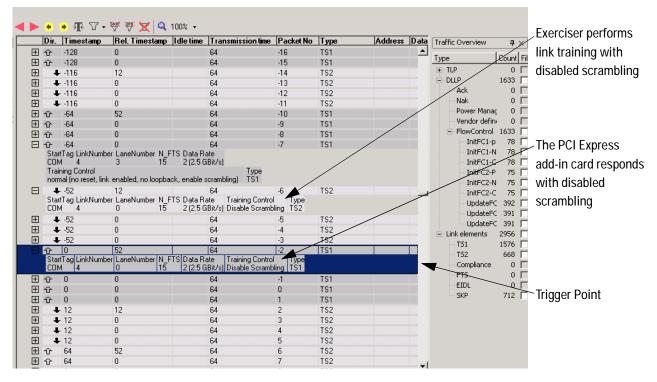

#### Figure 28 PCI Express Protocol Analyzer with Captured Traffic

In this case, the add-in card responds correctly to the error.

### Validating the System

Validating and optimizing your system means exhaustive stress tests, under maximum load, inserted errors and a range of different conditions.

The Protocol Exerciser gives you full and fast control over your test, from simple sequences to worst-case patterns, and, combined with the Protocol Analyzer, deeper investigation and increased test coverage.